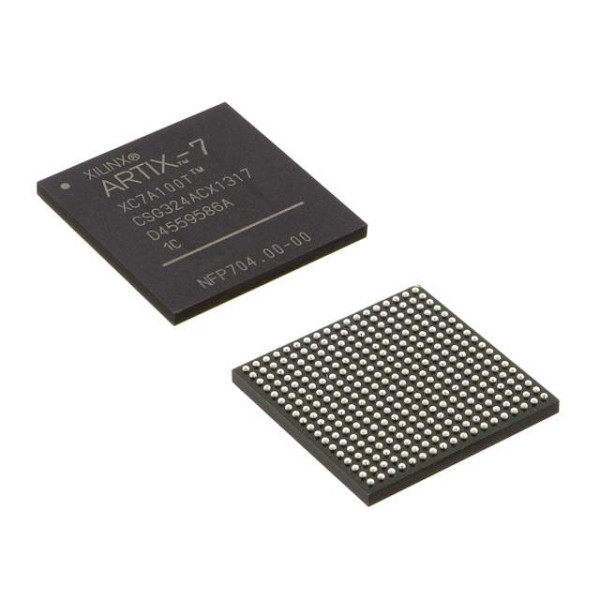

XC7A50T-2CSG324I FPGA – Feltprogrammerbar gate array XC7A50T-2CSG324I

♠ Produktbeskrivelse

| Produktattribut | Attributværdi |

| Fabrikant: | Xilinx |

| Produktkategori: | FPGA - Feltprogrammerbar Gate Array |

| Serie: | XC7A50T |

| Antal logiske elementer: | 52160 LE |

| Antal I/O'er: | 210 I/O |

| Forsyningsspænding - Min: | 0,95 V |

| Forsyningsspænding - Maks.: | 1,05 V |

| Minimum driftstemperatur: | - 40 grader Celsius |

| Maksimal driftstemperatur: | + 100°C |

| Datahastighed: | - |

| Antal transceivere: | - |

| Monteringsstil: | SMD/SMT |

| Pakke / Etui: | CSBGA-324 |

| Mærke: | Xilinx |

| Distribueret RAM: | 600 kbit |

| Indlejret blok-RAM - EBR: | 2700 kbit |

| Fugtfølsom: | Ja |

| Antal logiske arrayblokke - LAB'er: | 4075 LAB |

| Driftsforsyningsspænding: | 1 V |

| Produkttype: | FPGA - Feltprogrammerbar Gate Array |

| Fabrikspakke antal: | 1 |

| Underkategori: | Programmerbare logiske IC'er |

| Handelsnavn: | Artix |

| Enhedsvægt: | 28 g |

♠ Xilinx® 7-serien af FPGA'er omfatter fire FPGA-familier, der imødekommer hele spektret af systemkrav, lige fra lave omkostninger, lille formfaktor, omkostningsfølsomme applikationer med høj volumen til ultra-avanceret tilslutningsbåndbredde, logikkapacitet og signalbehandlingskapacitet til de mest krævende højtydende applikationer.

Xilinx® 7-serien af FPGA'er omfatter fire FPGA-familier, der imødekommer hele spektret af systemkrav, lige fra lave omkostninger, små formfaktor-, omkostningsfølsomme og store applikationer til ultra-avanceret tilslutningsbåndbredde, logikkapacitet og signalbehandlingskapacitet til de mest krævende højtydende applikationer. 7-serien af FPGA'er omfatter:

• Spartan®-7-serien: Optimeret til lave omkostninger, lavest strømforbrug og høj I/O-ydeevne. Fås i billig, meget lille formfaktorpakke for at opnå det mindste printkortfodaftryk.

• Artix®-7-serien: Optimeret til lavstrømsapplikationer, der kræver serielle transceivere og høj DSP- og logikgennemstrømning. Giver den laveste samlede materialepris til applikationer med høj gennemstrømning og omkostningsfølsomme applikationer.

• Kintex®-7-familien: Optimeret til den bedste pris-ydelse med en dobbelt så god forbedring i forhold til den foregående generation, hvilket muliggør en ny klasse af FPGA'er.

• Virtex®-7-familien: Optimeret til den højeste systemydelse og kapacitet med en dobbelt forbedring af systemydelsen. Enheder med den højeste kapacitet muliggjort af stablet siliciuminterconnect (SSI)-teknologi.

Bygget på en state-of-the-art, højtydende, lav-effekt (HPL), 28 nm, high-k metal gate (HKMG) procesteknologi, muliggør 7-seriens FPGA'er en uovertruffen stigning i systemydelsen med 2,9 Tb/s I/O-båndbredde, 2 millioner logikcellers kapacitet og 5,3 TMAC/s DSP, samtidig med at de forbruger 50% mindre strøm end tidligere generationers enheder og tilbyder dermed et fuldt programmerbart alternativ til ASSP'er og ASIC'er.

• Avanceret højtydende FPGA-logik baseret på ægte 6-input opslagstabelteknologi (LUT), der kan konfigureres som distribueret hukommelse.

• 36 Kb dual-port blok-RAM med indbygget FIFO-logik til databuffering på chippen.

• Højtydende SelectIO™-teknologi med understøttelse af DDR3-grænseflader på op til 1.866 Mb/s.

• Højhastigheds seriel tilslutning med indbyggede multi-gigabit transceivere fra 600 Mb/s til maksimale hastigheder på 6,6 Gb/s op til 28,05 Gb/s, der tilbyder en speciel lavstrømstilstand, optimeret til chip-til-chip-grænseflader.

• En brugerkonfigurerbar analog grænseflade (XADC), der inkorporerer dobbelte 12-bit 1MSPS analog-til-digital-konvertere med indbyggede termiske og forsyningssensorer.

• DSP-skiver med 25 x 18 multiplikator, 48-bit akkumulator og pre-adder til højtydende filtrering, inklusive optimeret symmetrisk koefficientfiltrering.

• Kraftfulde clock management tiles (CMT), der kombinerer faselåste loop (PLL) og blandede-tilstands clock manager-blokke (MMCM) for høj præcision og lav jitter.

• Implementer hurtigt integreret processorkraft med MicroBlaze™-processor.

• Integreret blok til PCI Express® (PCIe) til op til x8 Gen3 Endpoint- og Root Port-designs.

• Bredt udvalg af konfigurationsmuligheder, herunder understøttelse af standardhukommelser, 256-bit AES-kryptering med HMAC/SHA-256-godkendelse og indbygget SEU-detektion og -korrektion.

• Billig, wire-bond, bare-die flipchip-pakning med høj signalintegritet, der giver nem migrering mellem familiemedlemmer i samme pakke. Alle pakker er tilgængelige i blyfri og udvalgte pakker i blyfri variant.

• Designet til høj ydeevne og lavest mulig strømforbrug med 28 nm, HKMG, HPL-proces, 1,0 V kernespændingsprocesteknologi og 0,9 V kernespændingsmulighed for endnu lavere strømforbrug.