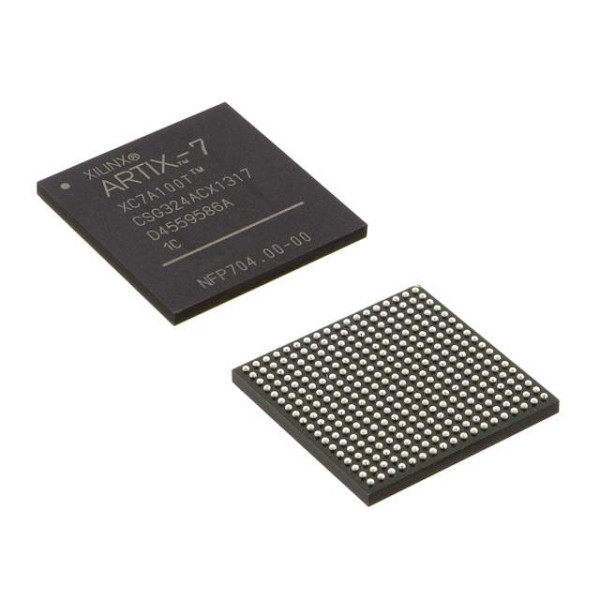

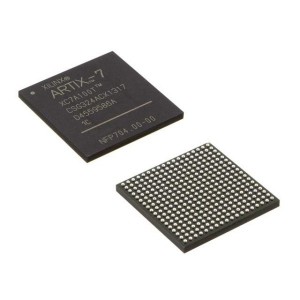

XC7A50T-2CSG324I FPGA – Feltprogrammerbar Gate Array XC7A50T-2CSG324I

♠ Produktbeskrivelse

| Produktegenskab | Attributværdi |

| Fabrikant: | Xilinx |

| Produktkategori: | FPGA - Field Programmable Gate Array |

| Serie: | XC7A50T |

| Antal logiske elementer: | 52160 LE |

| Antal I/O'er: | 210 I/O |

| Forsyningsspænding - min.: | 0,95 V |

| Forsyningsspænding - Max: | 1,05 V |

| Minimum driftstemperatur: | -40 C |

| Maksimal driftstemperatur: | + 100 C |

| Datahastighed: | - |

| Antal transceivere: | - |

| Monteringsstil: | SMD/SMT |

| Pakke/etui: | CSBGA-324 |

| Mærke: | Xilinx |

| Distribueret RAM: | 600 kbit |

| Embedded Block RAM - EBR: | 2700 kbit |

| Fugt følsom: | Ja |

| Antal logiske arrayblokke - LAB'er: | 4075 LAB |

| Driftsforsyningsspænding: | 1 V |

| Produkttype: | FPGA - Field Programmable Gate Array |

| Fabrikspakkemængde: | 1 |

| Underkategori: | Programmerbare logiske IC'er |

| Handelsnavn: | Artix |

| Enhedsvægt: | 1 oz |

♠ Xilinx® 7-seriens FPGA'er omfatter fire FPGA-familier, der imødekommer hele spektret af systemkrav, lige fra lavpris, lille formfaktor, omkostningsfølsomme applikationer med høj volumen til ultra avanceret tilslutningsbåndbredde, logisk kapacitet og signalbehandling kapacitet til de mest krævende højtydende applikationer

Xilinx® 7-seriens FPGA'er omfatter fire FPGA-familier, der imødekommer hele rækken af systemkrav, lige fra lavpris, lille formfaktor, omkostningsfølsomme applikationer med høj volumen til ultra-avanceret tilslutningsbåndbredde, logisk kapacitet og signalbehandlingskapacitet til de mest krævende højtydende applikationer.FPGA'erne i 7-serien inkluderer:

• Spartan®-7-familien: Optimeret til lave omkostninger, laveste effekt og høj I/O-ydelse.Tilgængelig i lavpris, meget lille formfaktoremballage til mindste PCB-fodaftryk.

• Artix®-7-familien: Optimeret til laveffektapplikationer, der kræver serielle transceivere og høj DSP og logisk gennemløb.Giver den laveste samlede stykomkostninger til højkapacitets, omkostningsfølsomme applikationer.

• Kintex®-7 Family: Optimeret til den bedste pris-ydelse med en 2X forbedring sammenlignet med tidligere generation, hvilket muliggør en ny klasse af FPGA'er.

• Virtex®-7 Family: Optimeret til den højeste systemydelse og kapacitet med en 2X forbedring af systemets ydeevne.Enheder med højest kapacitet aktiveret af stacked silicon interconnect (SSI) teknologi.

Bygget på en state-of-the-art, højtydende, lav-effekt (HPL), 28 nm, high-k metal gate (HKMG) procesteknologi, muliggør 7 serie FPGA'er en uovertruffen stigning i systemets ydeevne med 2,9 Tb/ s I/O-båndbredde, 2 millioner logiske cellers kapacitet og 5,3 TMAC/s DSP, mens de bruger 50 % mindre strøm end tidligere generationsenheder for at tilbyde et fuldt programmerbart alternativ til ASSP'er og ASIC'er.

• Avanceret højtydende FPGA-logik baseret på ægte 6-input lookup table (LUT) teknologi, der kan konfigureres som distribueret hukommelse.

• 36 Kb dual-port blok RAM med indbygget FIFO logik til databuffring på chip.

• Højtydende SelectIO™-teknologi med understøttelse af DDR3-grænseflader op til 1.866 Mb/s.

• Seriel højhastighedsforbindelse med indbyggede multi-gigabit transceivere fra 600 Mb/s til max.hastigheder på 6,6 Gb/s op til 28,05 Gb/s, der tilbyder en speciel laveffekttilstand, optimeret til chip-til-chip-grænseflader.

• Et brugerkonfigurerbart analogt interface (XADC), der inkorporerer dobbelte 12-bit 1MSPS analog-til-digital-konvertere med on-chip termiske og forsyningssensorer.

• DSP-slices med 25 x 18 multiplikator, 48-bit akkumulator og pre-adder til højtydende filtrering, inklusive optimeret symmetrisk koefficientfiltrering.

• Kraftige clock management fliser (CMT), der kombinerer faselåst sløjfe (PLL) og mixed-mode clock manager (MMCM) blokke for høj præcision og lav jitter.

• Implementer hurtigt indlejret behandling med MicroBlaze™-processor.

• Integreret blok til PCI Express® (PCIe), til op til x8 Gen3 Endpoint og Root Port-design.

• Bredt udvalg af konfigurationsmuligheder, herunder understøttelse af råvarehukommelser, 256-bit AES-kryptering med HMAC/SHA-256-godkendelse og indbygget SEU-detektering og korrektion.

• Billig, wire-bond, bare-die flip-chip og høj signalintegritet flipchip-emballage, der tilbyder nem migrering mellem familiemedlemmer i samme pakke.Alle pakker tilgængelige i Pb-fri og udvalgte pakker i Pb mulighed.

• Designet til høj ydeevne og laveste effekt med 28 nm, HKMG, HPL proces, 1,0V kernespændingsprocesteknologi og 0,9V kernespændingsmulighed for endnu lavere effekt.